‘1나노 반도체’ 앞당긴다… 원자층 트랜지스터 제조기술

- 권순용‧이종훈 신소재공학과 교수팀, 반도체-금속 간 1나노 수준 접합 소자 대면적화 성공

- 고성능 반도체 소자 미세화‧고집적화 탄력 기대… Nature Communications 게재

실리콘 아닌 다른 물질로 ‘더 싸고 작고 성능 좋은’ 반도체를 개발하는 ‘모어 무어(More Moore) 기술’에 탄력이 붙을 전망이다. 반도체 소자 속 반도체와 금속 사이를 ‘1나노미터(㎚, 10억 분의 1m)’ 이하로 줄이면서 고성능을 유지한 기술 덕분이다.

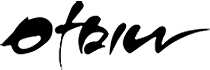

권순용·이종훈 신소재공학과 교수팀은 반도체 물질과 ‘초미세 금속 전극’이 0.7나노미터(원자 3개 크기)를 두고 수평으로 접합된 ‘고성능 초박막 반도체’ 소자를 원하는 형태로 합성(patterning)하는 데에 성공했다. 반도체 칩(Chip)의 성능을 높이려면 칩을 구성하는 개별 소자를 아주 작게 만들어야 하는데, 이를 해결하는 새로운 방법이 나온 것. ‘반도체 소자 미세화’를 앞당길 것으로 기대된다.

반도체 소자는 ‘전자가 원하는 때에 특정한 위치와 방향으로 움직’여야 제대로 작동한다. 그런데 칩 하나에 더 많은 소자를 넣으려 개별 소자를 작게 만들면, 전자가 원치 않는 위치로 흐르는 현상(터널링 효과)이 나타난다. 이 문제를 풀기 위해 ‘매우 얇은 2차원 반도체 물질’을 연구 중이지만, ‘그에 걸맞은 전극’은 나오지 않았다.

*예를 들어, 2차원 반도체 물질에 티타늄(Ti) 같은 일반 금속을 전극으로 쓰면 여러 결함이 생겨 성능이 저하된다. 또 일반 금속 전극은 크기가 클 뿐 아니라 전자 전송 길이(transfer length)가 수십~수백 나노미터 이상이라 반도체 소자의 전체 크기도 커진다. 결국, 고성능 초미세 반도체 소자를 구현하려면 이에 걸맞은 2차원 전극 물질도 새로 개발돼야 하는데, 이번 연구에서 이를 만족할 기술이 나왔다. 참고로, 전자 전송 길이는 금속과 반도체의 접합에서 실제로 전자가 이동할 수 있는 통로의 길이, 이 길이가 짧을수록 금속 전극의 미세화에 따른 반도체 소자의 성능 저하를 피하기 쉽다.

권순용·이종훈 교수팀은 고품질의 ‘2차원 반도체’에 걸맞은 ‘2차원 금속 전극’을 화학합성 과정에서 자연스럽게 맞붙도록 하는 방법을 찾았다. 2차원 반도체 물질인 ‘황화 몰리브데늄 화합물(MoS₂)’이 2차원 금속인 ‘텔루륨화 백금 화합물(PtTe₂)’의 가장자리 표면에서 화학적으로 합성되도록 한 것이다.

제1저자인 송승욱 UNIST 신소재공학과 박사는 “일반적인 2차원 금속은 고온에 불안정해 다양한 소자를 만들기 어렵지만, 2차원 텔루륨화 백금 화합물(PtTe₂)은 섭씨 825도의 고온에도 안정적이라 2차원 반도체가 합성되는 고온에서도 공정이 가능했다”며 “결함 없는 ‘2차원 반도체-금속 접합 소자’를 화학적 기상 증착법으로 구현한 기술”이라고 설명했다.

금속 전극 옆면 가장자리에 자연스럽게 반도체 물질이 합성되다 보니, 둘의 접합면은 원자 3개 크기로 얇고 소자 합성 과정에서 결함도 거의 발생하지 않았다. 이 덕분에 금속과 반도체 경계면의 에너지 장벽(쇼트키 배리어)이 이론치에 가깝게 아주 낮았고, 그만큼 전자 이동이 쉬워졌다. 이상적인 ‘쇼트키-모트 법칙(Schottky-Mott condition)’을 쉽게 따른 것이다.

*쇼트키-모트 법칙(Schottky-Mott condition): 금속과 반도체 물질이 접하면 생기는 에너지 장벽인 쇼트키 장벽(Schottky barrier)의 크기를 결정하는 이론. 실제 쇼트키 장벽이 이론값을 따라 갈 경우 외부 인자를 통해 장벽의 크기를 자유롭게 조절 할 수 있다

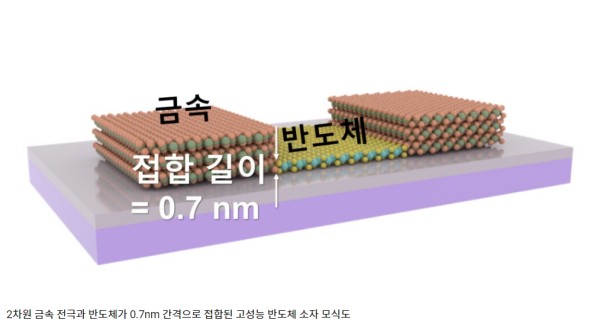

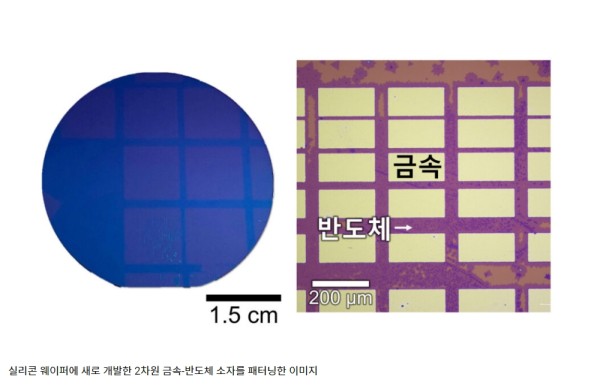

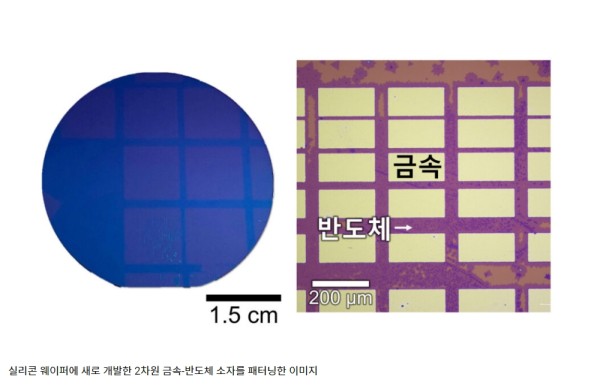

연구진은 이 기술을 이용해 2인치 상용 실리콘 웨어퍼(wafer)에 2차원 금속으로 패턴을 만들고, 이를 주형(template) 삼아 2차원 반도체를 화학적으로 조립했다. 이렇게 하면 2차원 반도체가 2차원 금속의 패턴을 따라 스스로 배열되면서 합성되므로 ‘정렬된 2차원 반도체-금속 접합 소자’를 구현할 수 있다. 기존처럼 조각 시편 수준이 아니라 상용 실리콘 웨이퍼 위에 대면적으로 제작하는 공정이라 상용화를 위한 대량생산에 더 가깝다.

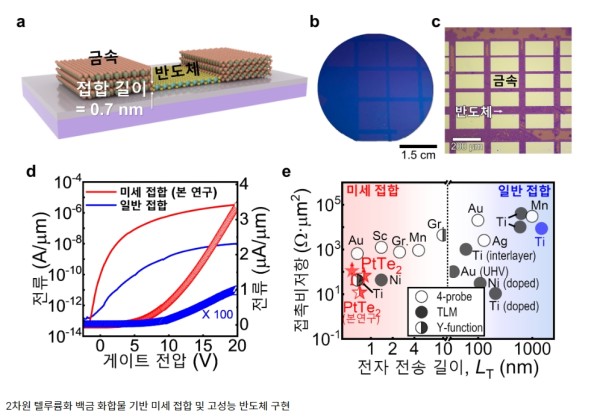

권순용 교수는 “수평형 금속-반도체 접합을 원하는 형태와 크기로 배열할 수 있어 반도체 크기에 따라 정교하고 체계적으로 소자 측정이 가능하다”며 “특히 원자층 트랜지스터 내 반도체-금속 간 접합의 접촉 비저항과 전자 전송 길이가 지금껏 구현된 2차원 소자 중에 가장 작아, 초미세 집적회로에서 우수한 성능을 갖는 차세대 반도체를 구현하는 데 도움 될 것”이라고 기대했다.

이 성과는 국제학술지 ‘네이처 커뮤니케이션스(Nature Communications)’ 8월 22일자에 출판됐으며, 과학기술정보통신부‧한국연구재단의 나노·소재기술개발사업 및 중견연구자지원사업과 IBS 다차원탄소재료연구단, UNIST 미래선도형 특성화사업에서 지원했다.

(a) 2차원 텔루륨화 백금 화합물을 활용한 차세대 반도체-금속 접합의 모식도.

금속과 반도체 간 접합 길이 0.7나노미터가 표현돼 있다.

(b) 2인치 기판상 대면적으로 합성된 패턴된 텔루륨화 백금 화합물의 사진

(c) 패턴된 텔루륨화 백금 화합물 금속을 주형으로 활용하여 합성된 정렬된 2차원 반도체-금속 접합 소자의 광학 사진

(d) 본 연구에서 구현된 트랜지스터 소자의 게이트 전압에 따른 전류를 나타내는 그래프. 미세 접합을 가진 반도체-금속 접합 소자가 훨씬 우수한 전류 수송 특성을 보여준다.

(e) 본 연구에서 구현된 미세 접합(PtTe₂)의 접촉비 저항 및 전자 전송길 이. 다른 연구 결과들에서 발표된 결과와 비교해 훨씬 낮은 접촉비 저항뿐만 아니라 전자 전송 길이를 가지고 있어 매우 작으면서도 우수한 성능의 반도체 소자로서 적용 가능함을 알 수 있다.

-------------------------------------------------------------

연구결과 개요

1. 연구배경

반도체 소자1)의 동작과 성능에서 ‘반도체(활성층)-금속(전극) 접합 특성’은 매우 중요하다. 서로 다른 두 물질의 계면 내 쇼트키 장벽(Schottky Barrier)2)의 존재 여부와 그 크기 및 제어 가능성은 소자의 성능과 전체 반도체 제작 공정에 영향을 주기 때문이다.

반도체 산업계는 2034년까지 반도체-금속 접합의 크기를 16나노미터 이하로 미세하게 만들어 집적회로 내 소자 밀도를 늘리고자 한다. 기존 실리콘 기반 반도체 소자는 활성층 영역에 이온 주입(ion implantation) 공정3)을 수행한 후 일반적인 금속 전극을 형성해 반도체-금속 접합 특성을 향상했다. 그러나 ‘모어 무어(More Moore) 반도체 소자’4)에서는 해당 이온 주입공정의 수행 자체가 물리적으로 불가능하다. 또 2차원 반도체 소재상에 일반적인 금속 전극을 형성할 경우, 반도체-금속 접합 계면에 다양한 형태의 불량이 발생할 뿐 아니라 전자 전송 길이(transfer length)가 길어 미세화된 소자의 성능이 열화될 수 있는 한계가 존재한다.

결함에 의한 높은 쇼트키 장벽과 장벽 높이 제어의 어려움을 해결하기 위해, 매우 얇은 두께의 수평형 접합을 형성하는 다양한 시도들이 활발하다. 그러나 상용화를 위해서는 원하는 위치와 형상을 제어하는 2차원 반도체-금속 접합 기술을 구현해 높은 수율과 고밀도 소자를 구현하는 것이 필수적이다. 그래핀뿐 아니라 여러 2차원 금속들을 접합 전극으로 활용한 몇몇 연구들이 기존에 이뤄졌으나, 균일한 형태 및 매우 얇은 접합 크기를 가진 반도체-금속 접합 소자 구현이 어렵고, 공정 도중 발생하는 결함이 전자 주입 효율에 악영향을 미치는 한계가 있었다.

이러한 한계를 극복하기 위해, 기상증착법을 통해 2차원 반도체와 2차원 금속이 수평으로 접합된 구조물을 합성으로 구현하는 연구가 수행됐다. 그러나 여러 2차원 물질들이 고온 환경에서 불안정할 뿐 아니라 2차원 반도체와 금속 상호 간의 격자 불일치로 인해 합성 결과물의 특성이 우수하지 못했다. 또한 매우 얇은 접합 크기를 유지하면서도 원하는 형태의 반도체-금속 접합 패턴을 만들기가 어려워서 실질적인 소자 구현 및 체계적인 특성 평가에 있어서 어려움이 많았다.

2. 연구내용

연구팀은 우수한 열적 안정성을 가진 ‘2차원 텔루륨화 백금 화합물(Platinum ditelluride, PtTe₂)’을 2차원 반도체인 황화 몰리브데늄 화합물((Molybdenum disulfide: MoS₂)의 접합 전극으로 활용하기 위한 2차원 금속-반도체 접합 소자 제조법을 세계 최초로 개발했다. 이 방법은 높은 온도(825℃)와 진공에서 2차원 전극이 안정할 뿐만 아니라, 회로를 그리는 상용 장비를 이용하여 원하는 형태로 원하는 위치에 합성할 수 있는 장점이 있다. 이렇게 얻어진 2차원 금속-반도체 접합 소자는 공정 중 야기되는 결함이 거의 없어 아주 우수한 물성들을 보였다.

무엇보다도, 티타늄과 같은 상용 금속 접합과 비교했을 때 2차원 금속-반도체 접합의 물리적 길이 및 전자수송길이5)가 0.7나노미터로 매우 짧았다. 접합 표면의 결함이 매우 작을 뿐 아니라, 매우 짧은 전자수송길이로 인해 쇼트키 장벽이 낮아져 전자주입 효율이 매우 우수했다. 예를 들어, 형성된 2차원 금속-반도체 간 접합의 접촉비 저항6)이 지금까지 연구개발된 2차원 소자들 중 가장 작아(~11.7Ω·μm2) 고성능의 차세대 반도체로서의 가능성을 보여줬다.

3. 기대효과

새롭게 개발된 성장공법은 금속-반도체 접합의 원하지 않는 불순물이나 합금화와 같은 결함이 없이도 원하는 형태의 소자를 획득할 수 있다. 이 점에서 더 자유로운 소자로서의 활용할 수 있다는 기대가 크다. 특히 본 연구에서 수행했던 소자 크기에 따른 정확한 성능 평가는 지금까지 합성 기술로는 구현될 수 없는 방법이다. 따라서 0.7나노미터의 매우 작은 크기를 가지며 접합돼 있는 소자의 전기적 특성을 더 잘 이해하는 데에 도움 줄 수 있다.

그뿐만 아니라 합성된 나노소재는 매우 얇고 투명하므로, 투명 유연 전자소자 등으로 활용될 수 있다. 또 나노소재의 물리적으로 독특한 에너지 밴드 성질 덕분에 전자 주입의 효율적 제어가 필요한 광스핀트로닉스 등 기초 연구 등에 기여할 수 있다.

-------------------------------------------------------------

용어설명

1. 반도체 소자

반도체 소자는 실리콘과 같은 반도체(전기 흐름을 조절하는 물질), 금속(도체, 전기가 잘 통하는 물질), 절연체(부도체, 전기가 안 통하는 물질) 등으로 구성돼 있다. 각종 전자제품에 들어가는 반도체 칩의 경우 단위 소자(회로) 여러 개가 집적돼 있다. 무어의 법칙(Moore's Law)은 2년 주기로 이 소자 집적도가 2배씩 향상된다는 것이다. 소자 집적도 높아지면 반도체의 정보 처리 속도 등이 빨라진다. 인텔(Intel)의 공동 설립자인 고든 무어(Gordon Earle Moore)가 1965년에 내놓은 것으로, 소자 집적의 한계로 인해 2016년 2월 무어의 법칙은 공식적으로 종말을 맞았다.

2. 쇼트키 장벽(Schottky barrier)

서로 다른 에너지 밴드를 갖는 금속과 반도체가 맞닿는 경우 전자가 넘어야 하는 에너지 장벽이 생긴다.

3. 모어 무어(More Moore) 반도체

상용화된 반도체 소자를 구성하는 실리콘 반도체 대신 그래핀과 같은 새로운 2차원 소재를 이용해 소자 집적 한계를 극복하려는 움직임을 뜻한다. 소자 집적도를 높이기 위해 회로 선폭을 좁히다 보면 ‘터널링 효과(tunneling effect)’가 발생한다. 나노미터(㎚, 10억 분의 1m)의 세계는 고전물리학이 아닌 양자역학이라는 법칙으로 움직이며, 전자 물질을 뚫고 통과하는 ‘터널링 효과(tunneling effect)’는 고밀도 집적회로를 개발하는 데에 큰 장애물이다. 이에 5㎚ 또는 그 이하의 회로 선폭을 가지는 칩을 만드는 것은 불가능하다고 여겨지게 됐다. 이를 극복하기 위해 업계에서는 실리콘이 아닌 새로운 반도체 재료로 칩 만들자는 ‘모어 무어(More Moore)’ 움직임이 시작됐다. 대표적인 후보 재료로는 그래핀과 같은 2차원 신소재를 들 수 있다.

4. 이온(전자) 주입 공정(ion implantation)

이온 주입공정을 통해 반도체(실리콘)의 전기전도도를 조절할 수 있다. 이온 주입공정을 통해 쇼트키 장벽을 넘는 전자의 숫자를 늘릴 수 있다

5. 전자 수송 길이(carrier’s transfer length)

금속과 반도체의 접합에서 실제로 전자가 이동 할 수 있는 통로의 길이. 전자 전송 길이가 짧을수록 금속 전극 및 접합 길이의 미세화에 따른 반도체 소자의 성능 저하를 피하기 쉽다.

6. 접촉비 저항(contact resistivity)

금속과 반도체의 접합에서 전자의 이동을 방해하는 정도를 나타내는 값. 접촉비저항이 낮을수록 더 많은 전자가 방해받지 않고 쉽게 이동할 수 있다.

-------------------------------------------------------------